北京时候 12 月 13 日早间动静,据报导,美国电脑芯片巨子英特尔旗下的“组件研讨团体”对外发布了多项新手艺,据称能够正在将来十年帮忙英特尔芯片不竭缩小尺寸、晋升机能,此中的一些手艺筹办将分歧芯片停止堆叠处置。

正在美国旧金山举行的一次国际半导体味议上,该团队经由过程多篇论文发布了上述新手艺。

曩昔几年,正在造造更小、更快速的芯片方面(所谓“X 纳米芯片”),英特尔输给了中国台湾的台积电和韩国三星电子两年夜敌手;现在,英特尔正正在想方设法从头博得芯片造造范畴的带领者职位。

此前,帕特・基辛格(Pat Gelsinger)担负英特尔信赖首席履行官以后,推出一系列正在 2025 年从头博得上风职位的贸易成长计划。而那一次该公司手艺团队推出了一系列“手艺性兵器”,帮忙英特尔正在 2025 年后一向连结手艺上风。

据报导,传统的芯片造造都是正在二维标的目的上,正在特定面积内整合更多晶体管。英特尔手艺团队提出了一个新的手艺冲破标的目的,那就是正在三维标的目的上堆叠“小芯片”(或“芯片瓦”),从而正在单元体积内整合更壮大的晶体管和计较才能。该公司展现的手艺显现,能够正在彼此叠加的小芯片上实现十倍于传统数目的通讯毗连管道,那也意味着将来小芯片一个叠加正在别的一个“身上”的空间很广漠。

半导体上 主要、 根基的组件是晶体管,它们相称于一个开关,代表数字逻辑系统的“1”或“0”状况。英特尔正在此次年夜会上发布的一项多是 主要的研讨功效,恰好展现了一种彼此堆叠晶体管的新手艺。

英特尔手艺团队暗示,经由过程晶体管堆叠手艺,可使得正在单元尺寸内整合的晶体管数目增加三成到五成。单元面积的晶体管数目越多,半导体的机能也就越壮大,那恰是环球半导体行业正在曩昔 50 多年时候里不竭成长的 主要缘由和纪律。

正在接管消息界采访时,英特尔“组件研讨团体”总监兼初级工程师保罗・费舍尔(Paul Fischer)暗示,经由过程把半导体零组件一个堆叠正在别的一个身上,英特尔手艺团队可节流芯片空间,“我们正削减芯片内部毗连通道的长度,从而节流能耗,如许不但进步芯片本前效益,更能加强芯片机能。”

版权声明:本文为原创文章,版权归 头条123 所有,欢迎 本文,转载请保留出处!

西南证券给予招商南油买入评级,受益于成品油跨区运输,调高目标价至7.2元,目标价格为7.2元

西南证券给予招商南油买入评级,受益于成品油跨区运输,调高目标价至7.2元,目标价格为7.2元 发改委:“双碳”工作开局良好 保持战略定力确保目标如期实现

发改委:“双碳”工作开局良好 保持战略定力确保目标如期实现 投资140亿元的抽水蓄能电站开工!协鑫能科: 终目标占据商用车换电市场30%以上市场份额

投资140亿元的抽水蓄能电站开工!协鑫能科: 终目标占据商用车换电市场30%以上市场份额 不止骁龙8!Redmi K50电竞版搭载自研读写引擎:拷

不止骁龙8!Redmi K50电竞版搭载自研读写引擎:拷 9月1日405只个股获券商关注 湘油泵目标涨幅达182.65%

9月1日405只个股获券商关注 湘油泵目标涨幅达182.65% 国金证券给予TCL中环买入评级 工业4.0打造核心竞争力 技术领先铸就盈利护城河 目标价格为69元

国金证券给予TCL中环买入评级 工业4.0打造核心竞争力 技术领先铸就盈利护城河 目标价格为69元 空头头寸达184亿美元!苹果超越特斯拉成华尔街头号做空目标

空头头寸达184亿美元!苹果超越特斯拉成华尔街头号做空目标 华安积极养老目标五年FOF正在发行

华安积极养老目标五年FOF正在发行 住建部:以保交楼保民生保稳定为首要目标 切实维护购房群众合法权益

住建部:以保交楼保民生保稳定为首要目标 切实维护购房群众合法权益 8月29日投资避雷针:1500亿整车龙头受限电影响 8月产销目标预计减量约10万辆

8月29日投资避雷针:1500亿整车龙头受限电影响 8月产销目标预计减量约10万辆 西南证券给予海光信息买入评级,供需两端同频共振,国产高端处理器腾飞,目标价格为70.16元

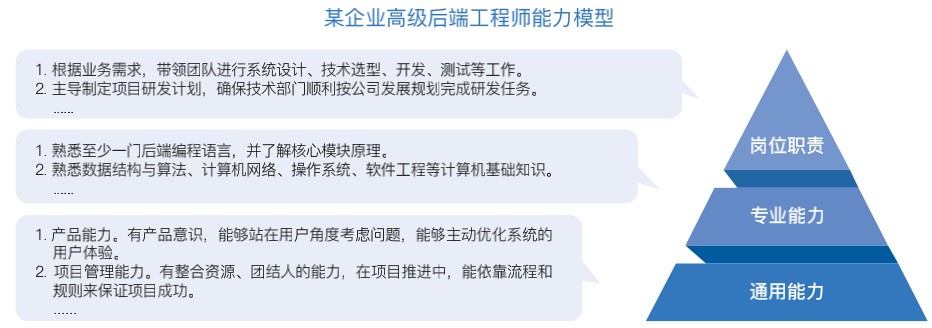

西南证券给予海光信息买入评级,供需两端同频共振,国产高端处理器腾飞,目标价格为70.16元 极客时间为目标人才培养提供 优方案

极客时间为目标人才培养提供 优方案 春天腹泻不止的缘故 应当如何调养

春天腹泻不止的缘故 应当如何调养 在河北承德考察时强调 贯彻新发展理念弘扬塞罕坝精神 努力完成全年经济社会发展主要目标任务

在河北承德考察时强调 贯彻新发展理念弘扬塞罕坝精神 努力完成全年经济社会发展主要目标任务 广期所助力“双碳”目标实现:年内推出工业硅期货 加快铂、钯等期货品种上市

广期所助力“双碳”目标实现:年内推出工业硅期货 加快铂、钯等期货品种上市 中国2015年GDP增长目标7%左右 CPI涨幅3%

中国2015年GDP增长目标7%左右 CPI涨幅3% 不止性能拉满 飞行堡垒8加持正版Windows10全速起航

不止性能拉满 飞行堡垒8加持正版Windows10全速起航 廊坊银行总资产规模突破2780亿 超额完成全年任务目标

廊坊银行总资产规模突破2780亿 超额完成全年任务目标 8月29日399只个股获券商关注 中兴通讯目标涨幅达149.17%

8月29日399只个股获券商关注 中兴通讯目标涨幅达149.17% 海南:35项措施推动经济恢复提振 冲刺全年经济发展目标

海南:35项措施推动经济恢复提振 冲刺全年经济发展目标